## In-Situ De-embedding (ISD)

Ching-Chao Huang huang@ataitec.com

January 31, 2018

## Outline

- What is causality

- What is In-Situ De-embedding (ISD)

- Comparison of ISD results with simulation and other tools

- How non-causal de-embedding affects connector compliance testing

- How to extract accurate PCB trace attenuation that is free of spikes and glitches

- How to extract a PCB's material property (DK, DF, roughness) by matching all IL, RL, NEXT, FEXT and TDR/TDT of de-embedded PCB traces

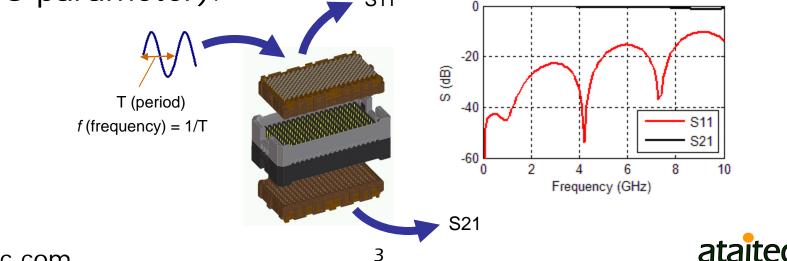

## **VNA and S parameter**

- Vector network analyzer (VNA) is an equipment that launches a sinusoidal waveform into a structure, varies the period (or frequency) of waveform, and lets us observe the transmitted and reflected wave as "frequency-domain response".

- Such frequency-domain response, when normalized to the incident wave, is called scattering parameter (or, S parameter).

## What is **S** parameter

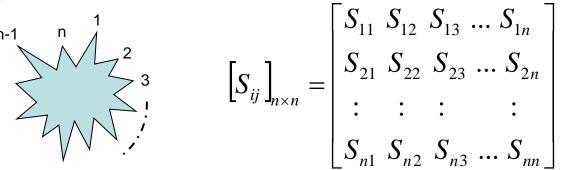

For an n-port (or I/O) device, S parameter is an n x n matrix:

- $S_{ij}$  is called the S parameter from Port *j* to Port *i*.

- S<sub>ij</sub> has a unique property that its magnitude is less than or equal to 1 (or, 0 dB) for a passive device.

$$\begin{aligned} \left| S_{ij} \right| &\leq 1 \\ S_{ij} \left( dB \right) &= 20 \times \log_{10} \left| S_{ij} \right| &\leq 0 \quad dB \end{aligned}$$

## What is a Touchstone (.sNp) file

S parameter at each frequency is expressed in Touchstone file format.

in GHz in dB and Reference phase angle S param impedance Total number of ports = 4! Total number of frequency points = 800 # GHZ S DB R 50 -41.40676 79.91354 -0.08648679 -6.544144 0.025 48.77486 -105.618-36.59296 -49.5004579.94686 -36.35592 51.52433 -49.4886 -6.527076 -41.39364-105.5124-0.09038406 -0.08421237 -6.537903-49.4481479.91856 -105.644-36.031749.60022 -41.37105-105.8186 -6.542909 -41.36758 48.98348 -49.44393 -0.0983413679.9318 -36.05645 0.05 -32.2257648.03161 -35.5939474.15976 -0.1277169-12.82876-43.90183-112.099574.16304 -32.12694 50.92389 -43.90926 -112.0764 -12.7985-35.58736 -0.132402-0.1242117 -12.82302 -43.89-112.0248 -32.1098750.3115 -35.56998 74.078 -43.88424 -112.0517 -0.1381616 -12.80199 -35.56758 74.06782 -31.94136 50.49276 0.075 -29.88861 42.02766 -32.19713 -40.67476 68.06704 -0.1589249 -19.05252-118.8188 -32.19116 68.0941 -29.7086 -40.63857-118.837-19.01593 45.41557 -0.1635606 -0.1603356 -19.0376 -40.63557 -118.8543 -29.89064 47.63852 -32.16917 67.94677 -0.1737256 -40.65711 -118.8021 -19.02956 -32.1686567,93389 -29.6544446.15548 : : : Frequency in GHz S11, S12, ..., S44 in dB and phase angle

ataitec

## What is causality

## cau-sal-i-ty

/kô'zalədē/

noun

- 1. the relationship between cause and effect.

- 2. the principle that everything has a cause.

In other words:

Can not get something from nothing.

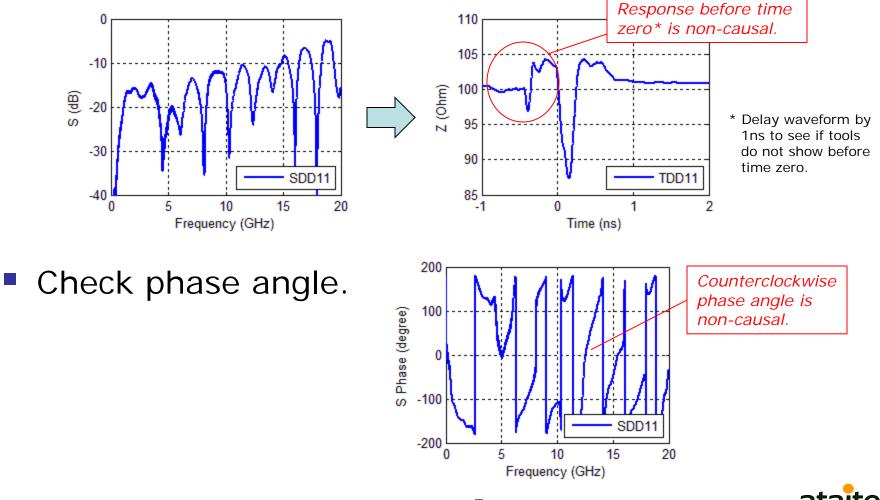

## How to identify non-causal S parameter

Convert S parameter into TDR/TDT.

## Why does S parameter violate causality

- Measurement error (de-embedding), simulation error (material property) and finite bandwidth of S parameter all contribute to non-causality.

- Kramers-Kronig relations require that the real and imaginary parts of an analytic function be related to each other through Hilbert transform:

$$\Psi(\omega) = \Psi_R(\omega) + j\Psi_I(\omega)$$

$$\Psi_R(\omega) = \frac{1}{\pi} P \int_{-\infty}^{\infty} \frac{\Psi_I(\omega')}{\omega' - \omega} d\omega'$$

$$\Psi_I(\omega) = -\frac{1}{\pi} P \int_{-\infty}^{\infty} \frac{\Psi_R(\omega')}{\omega' - \omega} d\omega'$$

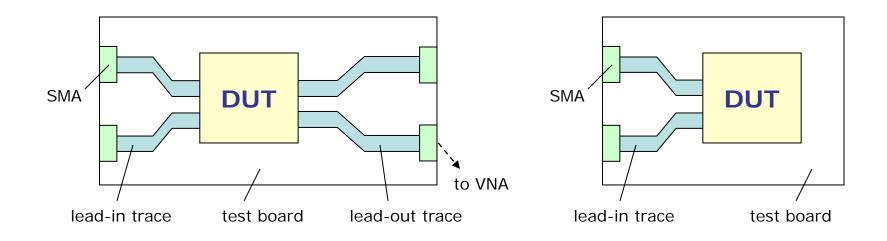

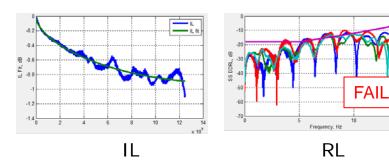

## What is de-embedding

To remove the effect of fixture (SMA connector + lead-in/out) and extract the S parameter of DUT (device under test).

- The lead-ins and lead-outs don't need to look the same.

- There may even be no lead-outs (e.g., package).

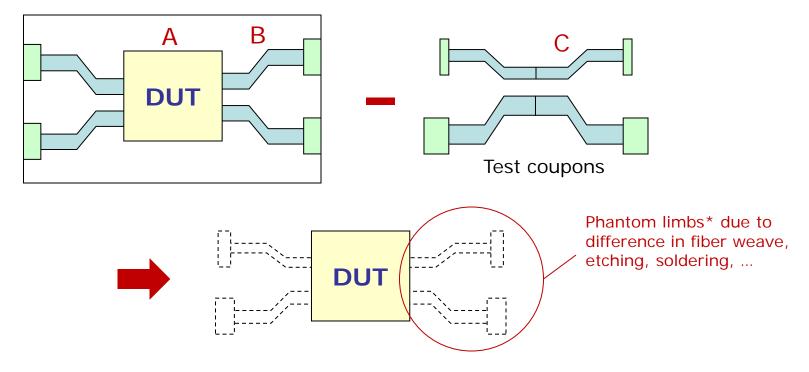

# Why do most de-embedding tools give causality error

Most tools use test coupons directly for deembedding, so difference between actual fixture and test coupons gets piled up into DUT results.

\* http://www.edn.com/electronics-blogs/test-voices/4438677/Software-tool-fixes-some-causality-violations by Eric Bogatin

## What is In-Situ De-embedding (ISD)

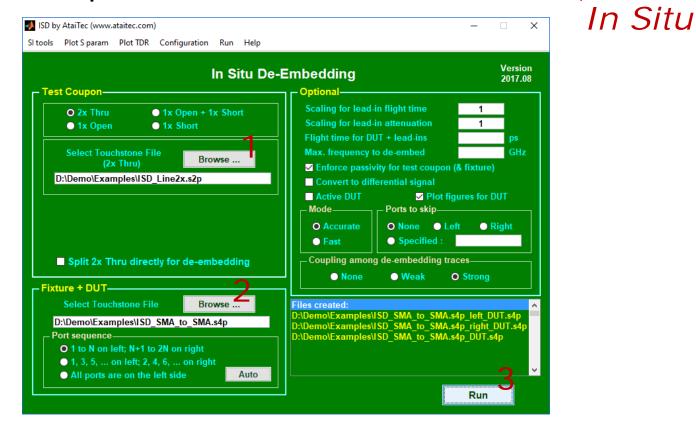

Use "2x thru" or "1x open / 1x short" as reference and de-embed <u>fixture's actual impedance</u> through numerical optimization.

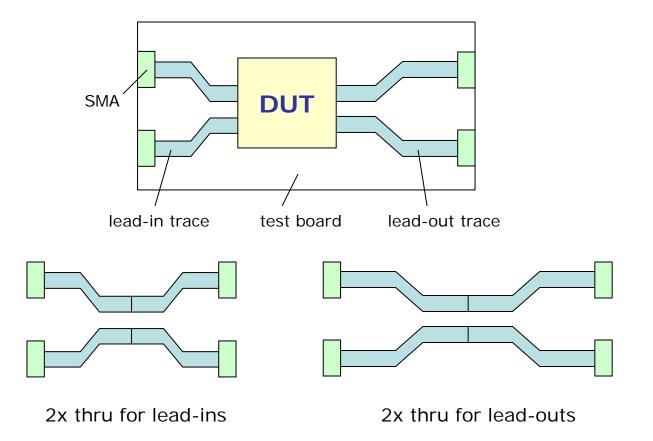

## What is "2x thru"

"2x thru" is 2x lead-ins or lead-outs.

2 sets of "2x thru" are required for asymmetric fixture.

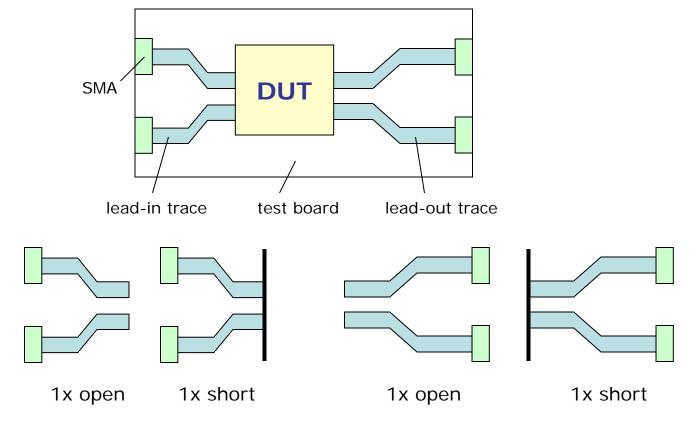

## What is "1x open / 1x short"

"1x open / 1x short" is useful when "2x thru" is not possible (e.g., connector vias, package, ...).

## Why ISD is more accurate and saves \$\$\$

- More board space Multiple test coupons are required.

- Test coupons are used directly for deembedding.

- All difference between calibration and actual DUT boards gets piled up into DUT results.

- Expensive SMAs, board materials (Roger) and tight-etching-tolerance are required.

- Impossible to guarantee all SMAs and traces are identical (consider weaves, etching, ...)

- Time-consuming manual calibration is required.

- Reference plane is in front of DUT.

# ISD test coupon ISD test coupon ISD test coupon Only one 2x thru test coupon is needed. Test coupon is used only for reference, not for direct de-embedding. Actual DUT board impedance is de-embedded.

- Inexpensive SMAs, board materials (FR4) and loose-etching-tolerance can be used.

- ECal can be used for fast SOLT calibration.

- Reference plane is in front of SMA.

- De-embedding requires only two input files: 2x thru and DUT board (SMA-to-SMA) Touchstone files.

- More information: Both de-embedding and DUT files are provided as outputs.

\* TRL = Thru-Reflect-Line

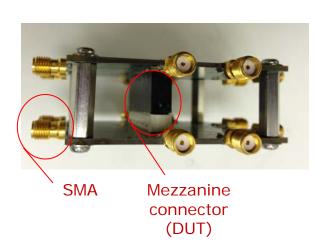

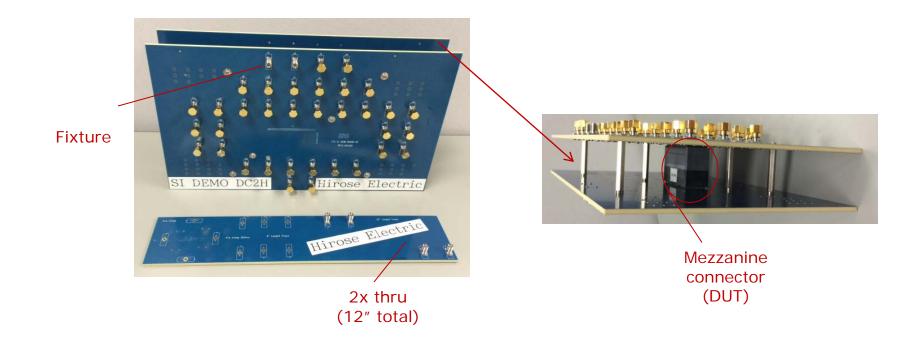

## Example 1: Mezzanine connector ISD vs. TRL

In this example, we will use ISD and TRL to extract a mezzanine connector and compare their results.

\*Courtesy of Hirose Electric

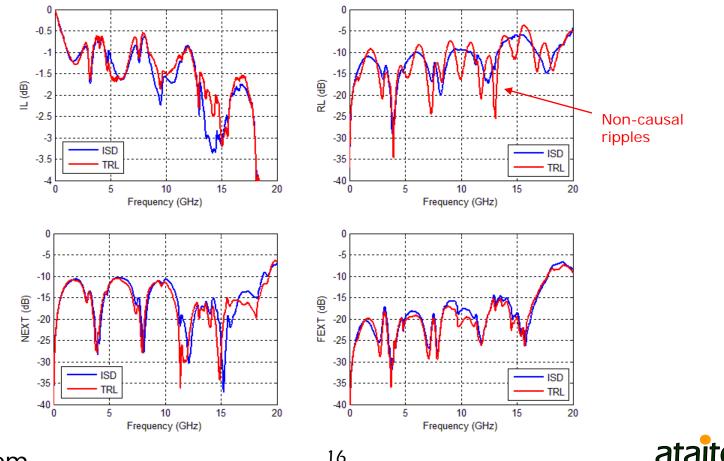

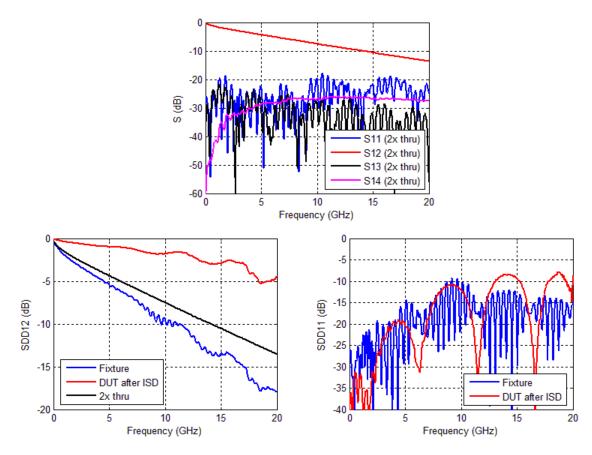

### **DUT results after ISD and TRL** Which one is more accurate?

TRL gives too many ripples in return loss (RL) for such a small DUT.

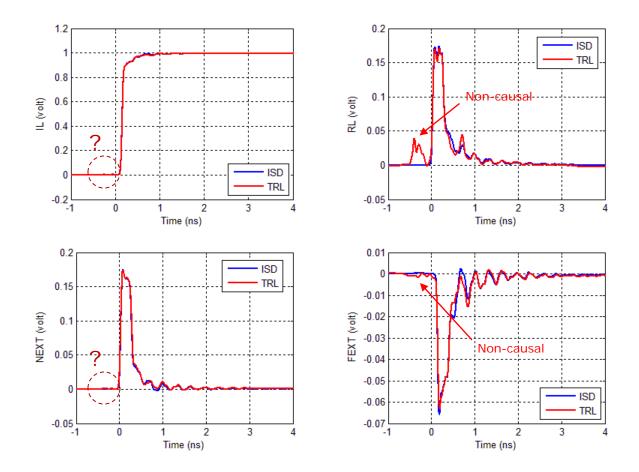

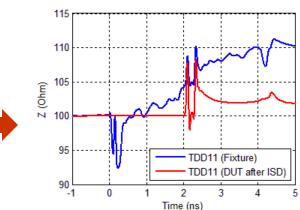

# Converting S parameter into TDR/TDT shows non-causality in TRL results

Rise time = 40ps (20/80)

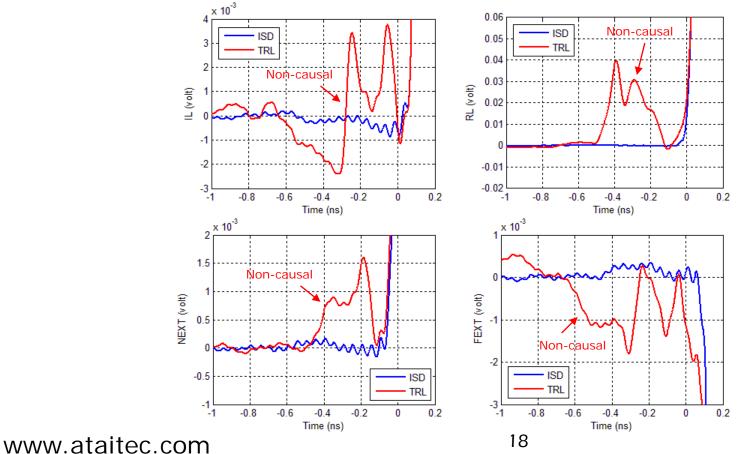

# Zoom-in shows non-causal TRL results in all IL, RL, NEXT and FEXT

TRL causes time-domain errors of 0.38% (IL), 25.81% (RL), 1.05% (NEXT) and 2.86% (FEXT) in this case\*.

\* The percentage is larger with single-bit response and/or faster rise time.

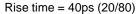

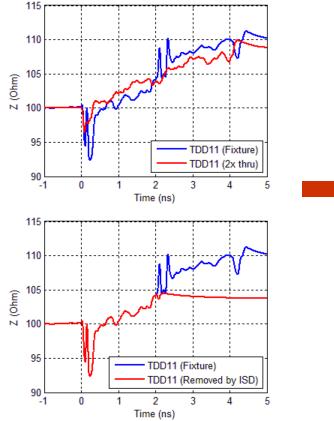

## How did ISD do it?

Through numerical optimization, ISD de-embeds fixture's impedance exactly, independent of 2x thru's impedance.

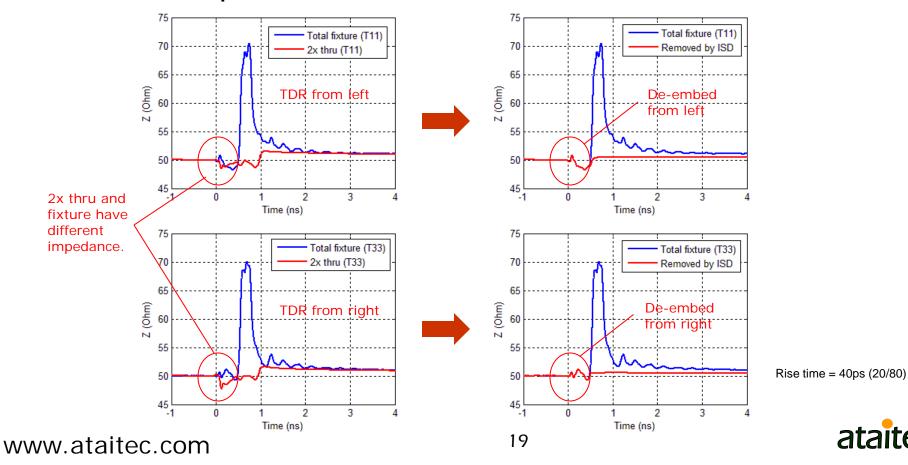

## TRL can give huge error in SDD11 even with small impedance variation\*

ISD is able to de-embed fixture's differential impedance with only a single-trace 2x thru.

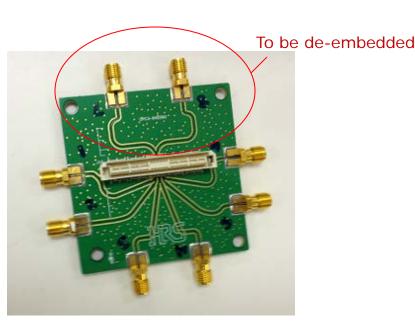

## **Example 2: Mezzanine connector** *Extracting DUT from a large board*

TRL is impractical for de-embedding large and coupled lead-ins/outs.

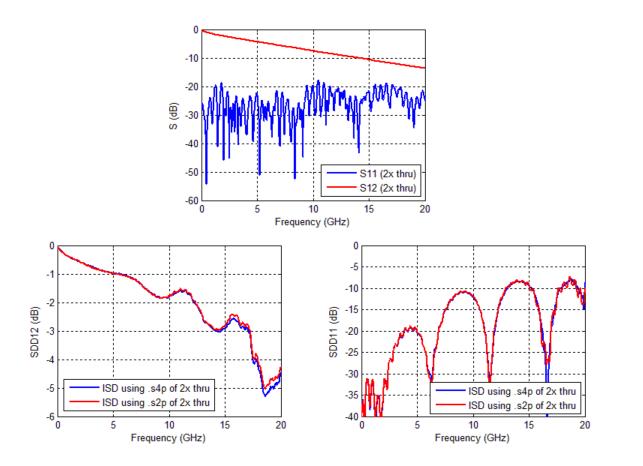

# ISD can use a .s4p file of 2x thru for de-embedding

TRL would have required many long and coupled traces.

## ISD can even use a .s2p file of 2x thru to de-embed crosstalk...

And the results are similar!

# ISD allows a large demo board to double as a characterization board

ISD de-embeds fixture's impedance regardless of 2x thru's impedance.

Rise time = 40ps (20/80)

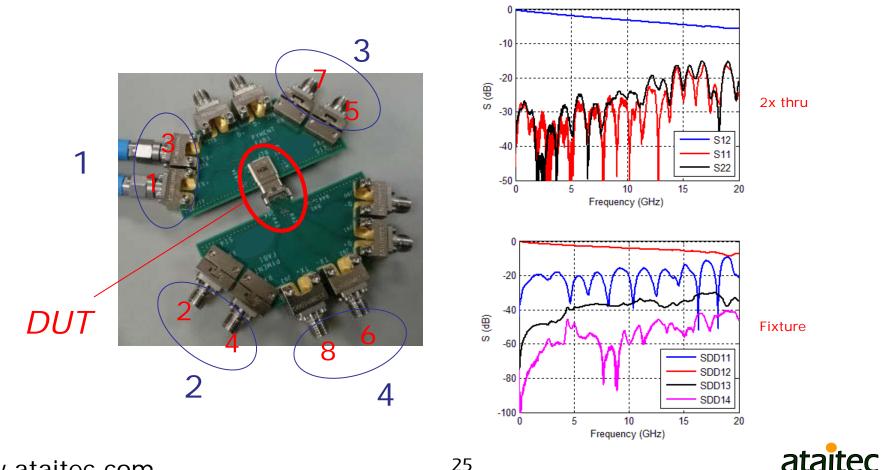

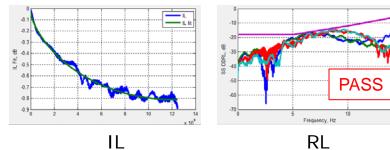

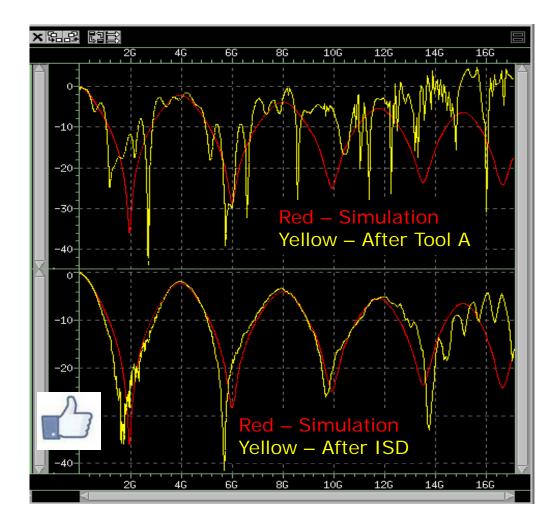

## **Example 3: USB type C mated connector** ISD vs. Tool A

Good de-embedding is crucial for meeting compliance spec.

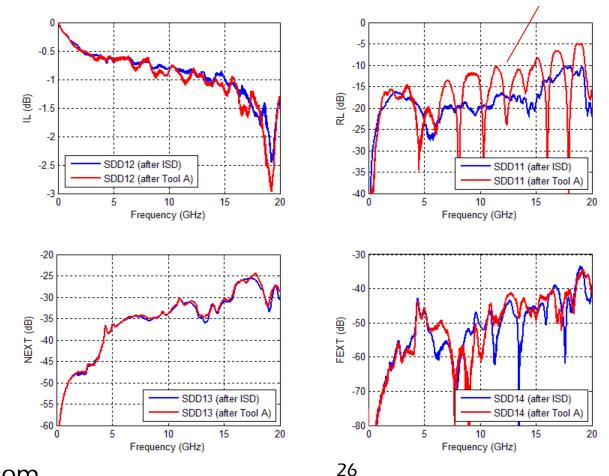

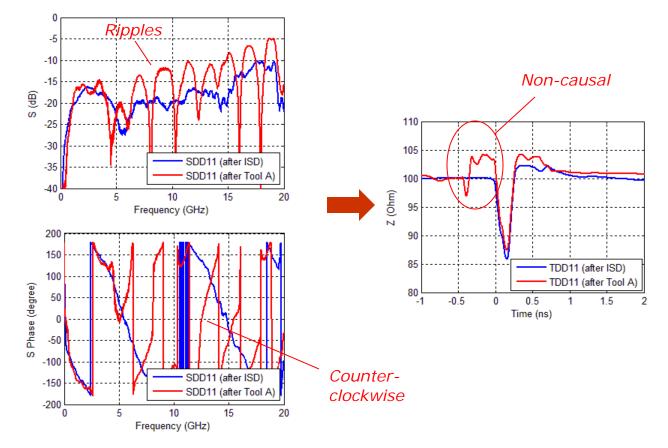

### **DUT results after ISD and Tool A** *Which one is more accurate?*

Tool A gives too many ripples in return loss (RL) for such a small DUT.

Non-causal ripples

www.ataitec.com

# Converting S parameter into TDR/TDT shows non-causality in Tool A results

Counter-clockwise phase angle is another indication of non-causality.

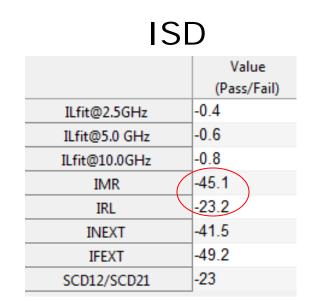

# De-embedding affects pass or fail of compliance spec.

ISD improves IMR and IRL (from compliance tool).

| 1001 A  |         |             |      |

|---------|---------|-------------|------|

|         |         | Value       |      |

|         |         | (Pass/Fail) | Spec |

| ILfit@  | 2.5GHz  | -0.4        | -0.6 |

| ILfit@! | 5.0 GHz | -0.6        | -0.8 |

| ILfit@1 | .0.0GHz | -0.9        | -1.0 |

| IN      | ИR      | -43.7       | -40  |

| I       | રા      | -20.8       | -18  |

| IN      | EXT     | -41.5       | -44  |

| IF      | EXT     | -49.3       | -44  |

| SCD12   | /SCD21  | -23.2       |      |

|         |         |             |      |

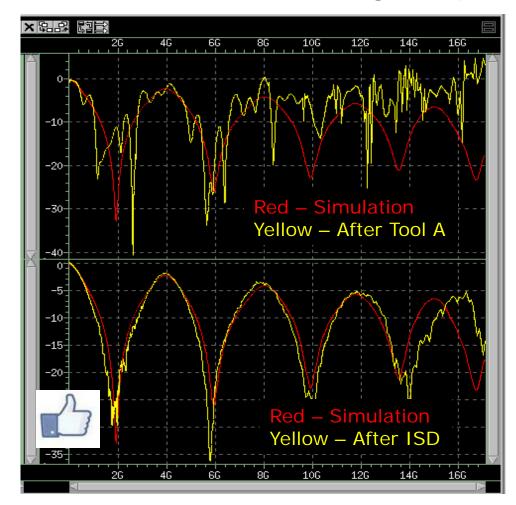

## Example 4: Resonator ISD vs. Tool A vs. simulation

Good de-embedding is crucial for design verification (i.e., correlation) and improvement.

## **SDD11** *ISD correlates with simulation*

## SCC11 ISD correlates with simulation

Good correlation is crucial for design improvement.

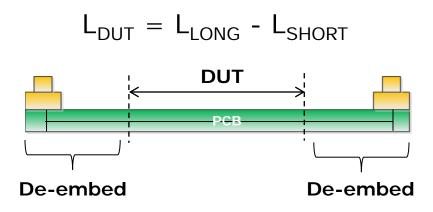

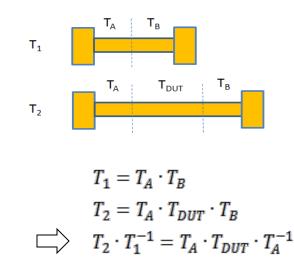

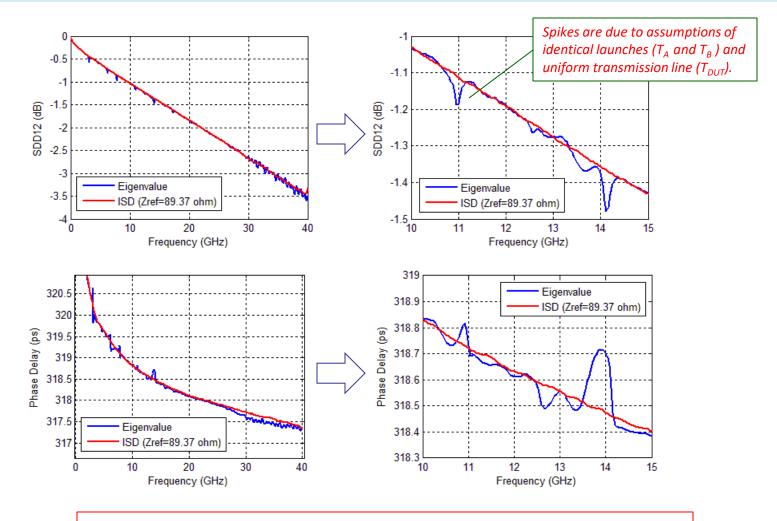

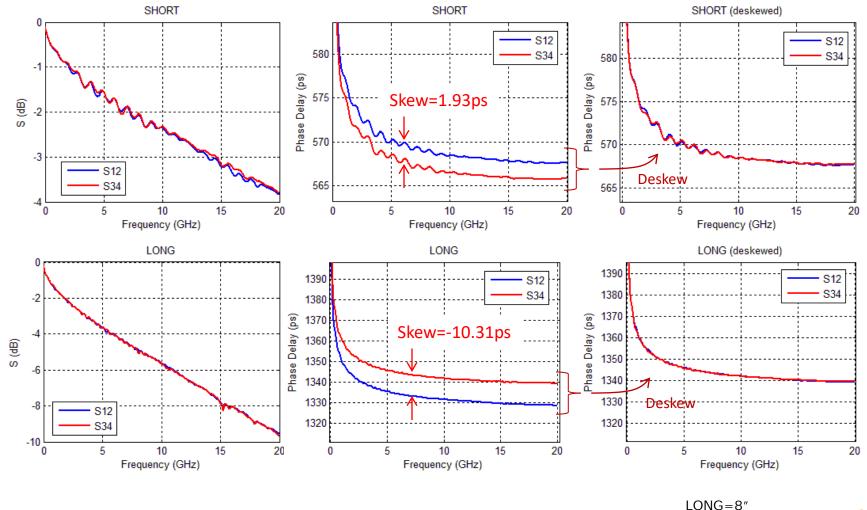

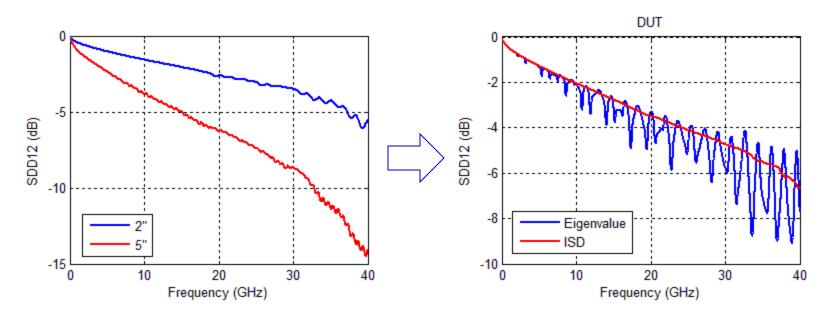

## **Example 5: PCB trace attenuation** *ISD vs. eigenvalue (Delta-L)*

De-embed short trace (+ launch) from long trace (+ launch) to get trace-only attenuation.

### **Eigenvalue solution: not de-embedding** *For calculating trace attenuation only*

- Convert S to T for short and long trace structures

- Assume the left (and right) sides of short and long trace structures are identical

- Assume DUT is uniform transmission line

- Trace-only attenuation is written in one equation.

For uniform transmission line:  $T_{DUT} = P \cdot \begin{pmatrix} e^{-\gamma l} & 0 \\ 0 & e^{+\gamma l} \end{pmatrix} \cdot P^{-1}$ Let  $T_2 \cdot T_1^{-1} = \begin{pmatrix} a & b \\ c & d \end{pmatrix}$   $\implies e^{-\gamma l} = \frac{(a+d) \pm \sqrt{(a-d)^2 + 4bc}}{2}$ eigenvalue modal propagation constant

#### Case 1: 2" (=7"-5") trace attenuation Eigenvalue solution is prone to spikes

ISD's spike-free results help DK and DF extraction later.

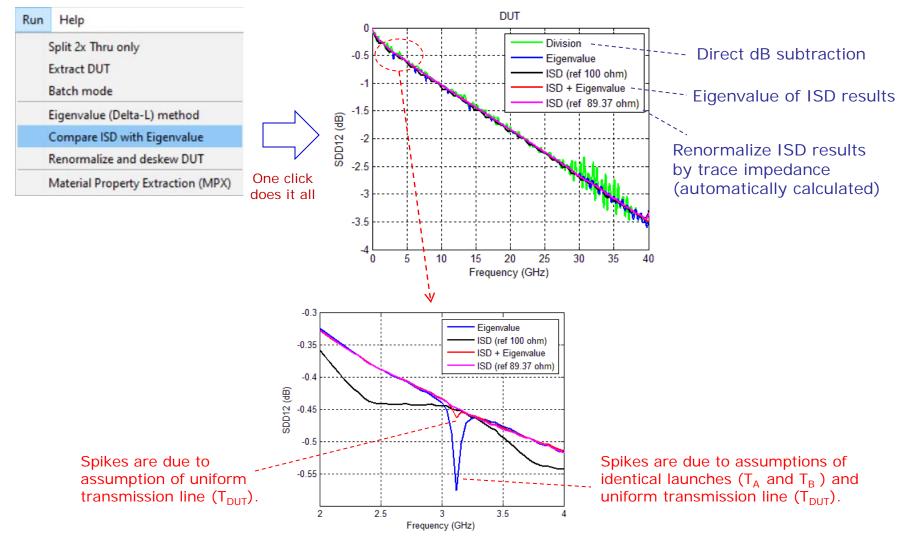

# One click compares ISD with eigenvalue and more...

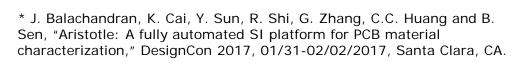

#### How to define trace impedance PCB trace is non-uniform transmission line

Define impedance by minimal RL\*

[S]

S11

$\varphi = \int_{f_{\min}}^{f_{\max}} \left\{ \left| S_{11}(f) \right|^2 + \left| S_{22}(f) \right|^2 \right\} \cdot \left| w(f) \right|^2 df$

$w(f) = \frac{\sin(\pi f T_r)}{\pi f T} \cdot \frac{\sin(\pi f T_b)}{\pi f T_c}$

$\Rightarrow^{T_r}$

$\in T_h$  \*

Minimize:

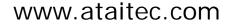

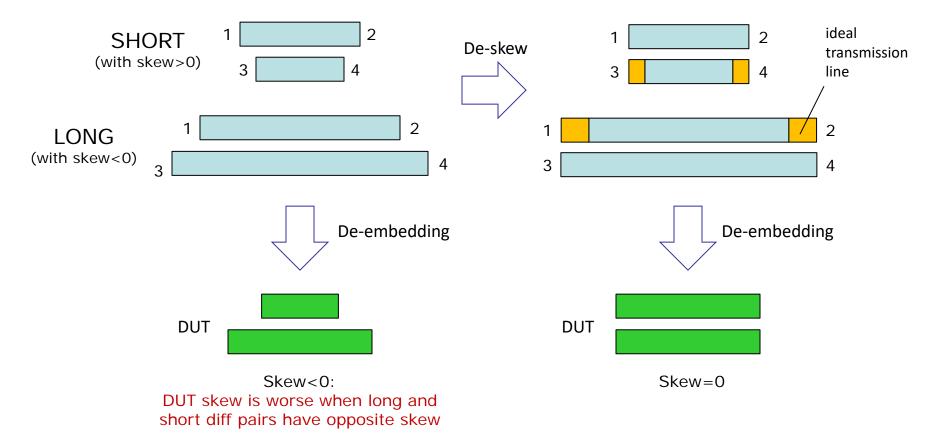

## **Skewless de-embedding**

Pad ideal transmission line to de-skew.

# ISD optionally automates de-skewing of raw data

www.ataitec.com

LONG=8" SHORT=3"

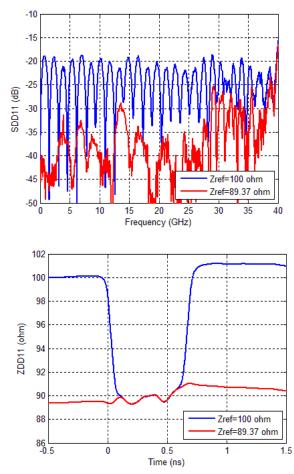

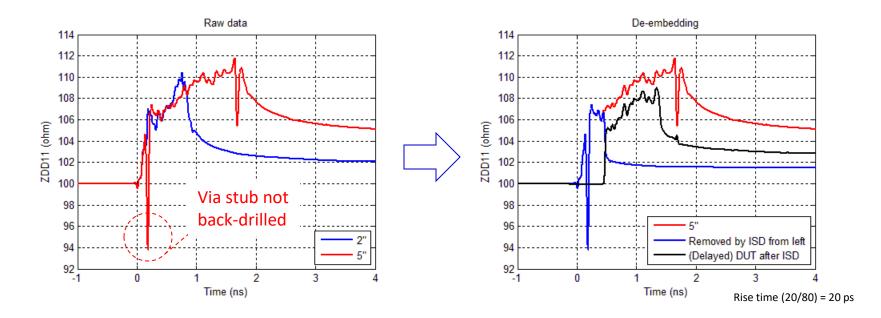

# Case 2: Extracted trace attenuation can be very different with or without skew

# Case 3: Eigenvalue (Delta-L) solution becomes unstable in this case, but why?

#### TDR of raw data reveals why... 2" structure was back-drilled but 5" was not

- Eigenvalue solution assumes 2" and 5" structures have identical launches.

- ISD de-embeds 5" structure's launch correctly.

ISD saves \$\$\$ and time for not spinning another board.

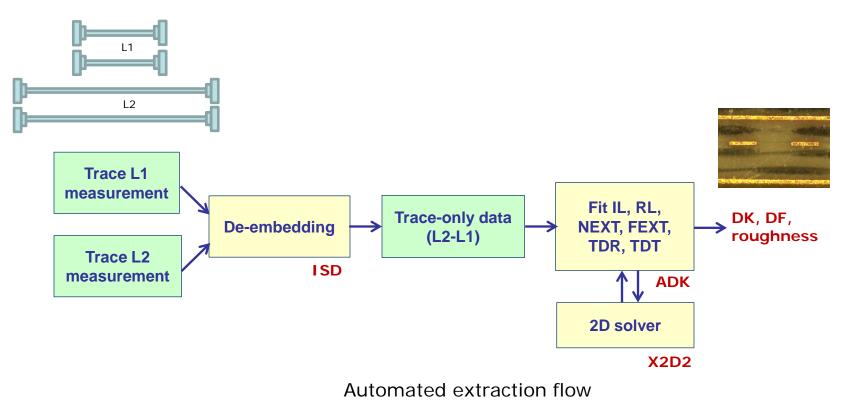

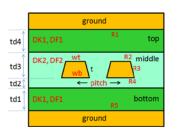

#### **Example 6: Material property extraction** *DK, DF and roughness*

Self consistent approach to extract DK, DF and roughness by matching all IL, RL, NEXT, FEXT and TDR/TDT of de-embedded trace-only data.

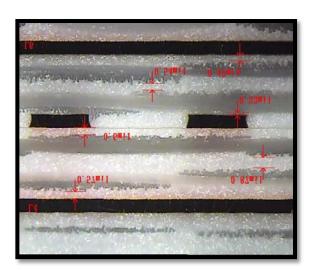

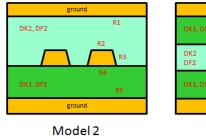

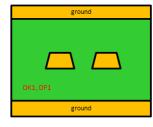

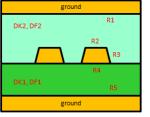

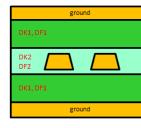

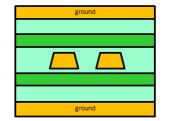

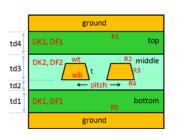

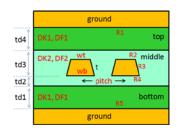

#### **Models for cross section**

Model 1

Optimized variables: DK1, DF1, DK2, DF2 R1, R2, R3, R4, R5 (roughness) Metal width and spacing

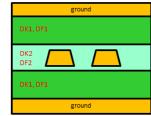

Model 3

ground

Model 5

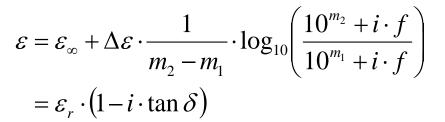

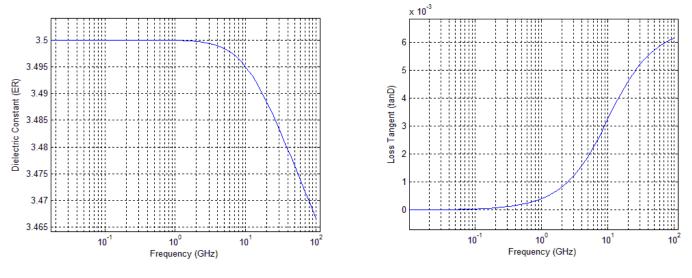

### **Causal dielectric model**

- Wideband Debye (or Djordjevic-Sarkar) model

- Need only four variables:  $\varepsilon_{\infty}$  ,  $\Delta \varepsilon$  ,  $m_1$  ,  $m_2$

$\varepsilon_{\infty}=3.35$  ,  $\Delta\varepsilon=0.15$  ,  $m_{1}=10$  ,  $m_{2}=14.5$

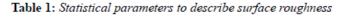

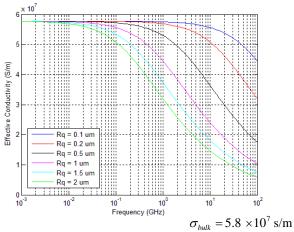

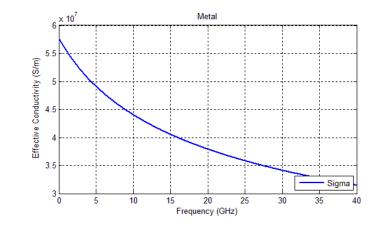

# Surface roughness model

Effective conductivity (by G. Gold & K. Helmreich at DesignCon 2014) needs only two variables:  $\sigma_{\rm bulk}$ ,  $R_q$

| Parameter | Description               | Standard                     |

|-----------|---------------------------|------------------------------|

| Rq        | root mean square          | DIN EN ISO 4287              |

| Ra        | arithmetic average        | DIN EN ISO 4287, ANSI B 46.1 |

| Rk        | core roughness depth      | DIN EN ISO 13565             |

| Rz        | average surface roughness | DIN EN ISO 4287              |

• Numerically solving  $\nabla^2 \overline{B} - j\omega\mu\sigma\overline{B} + \frac{\nabla\sigma}{\sigma} \times (\nabla \times \overline{B}) = 0$  and equating power to that of smooth surface gives  $\sigma_{eff}$

- ✤ Simple

- Work well with field solver

- Give effect of roughness on all IL, RL, NEXT and FEXT

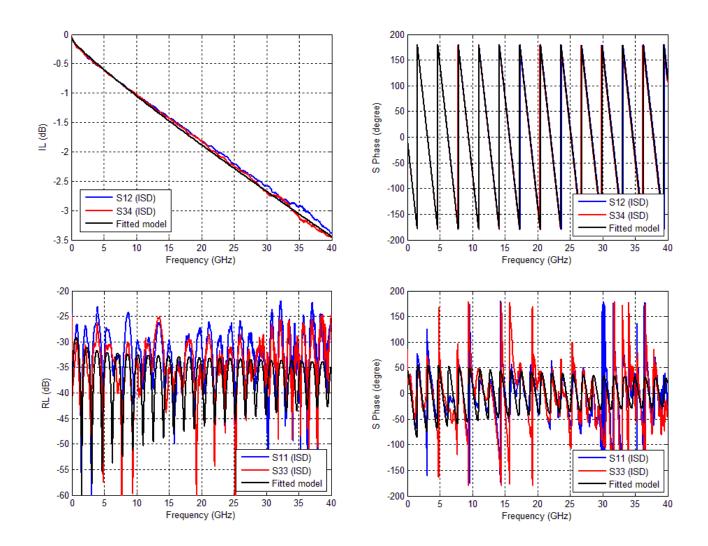

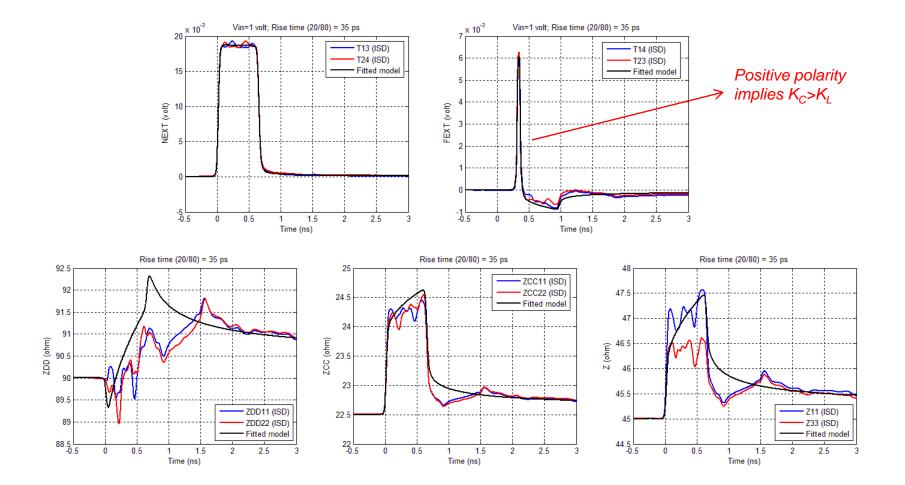

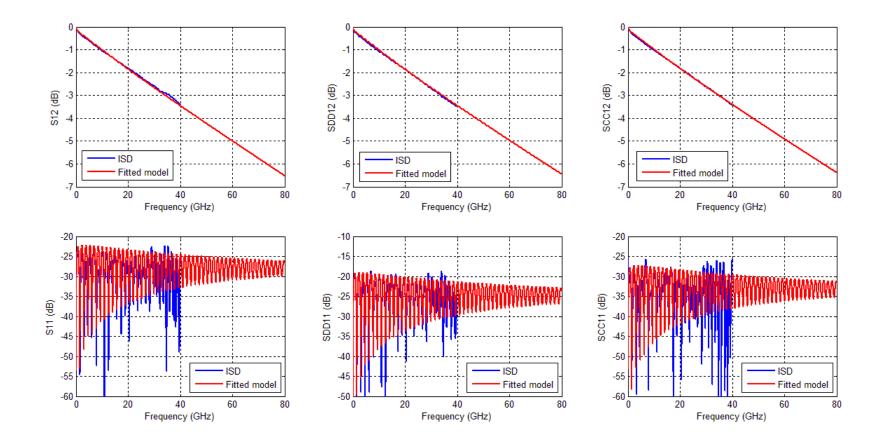

## Matching IL and RL

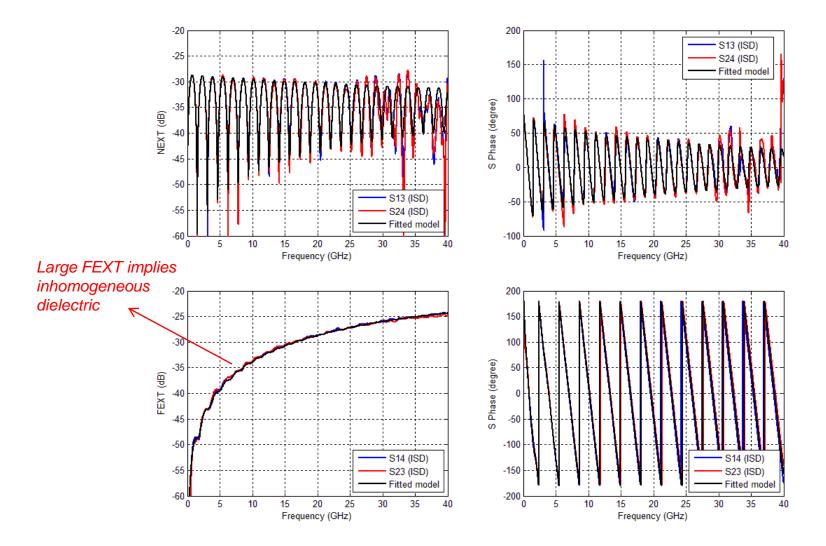

## Matching NEXT and FEXT

ataitec

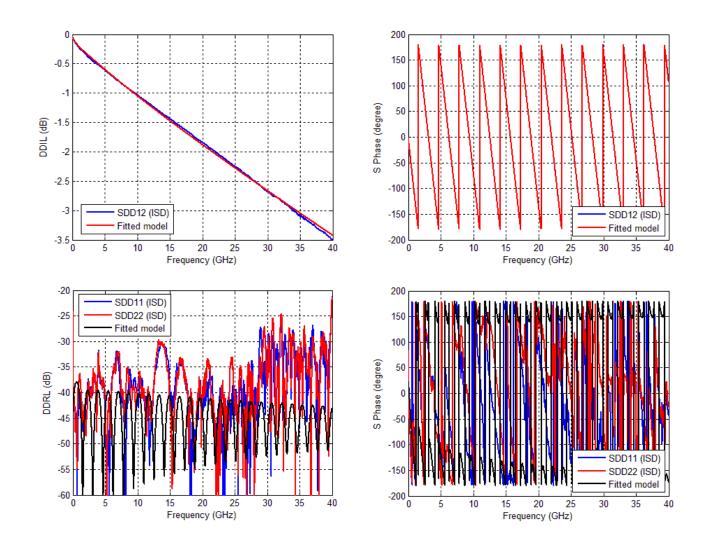

## Matching DDIL and DDRL

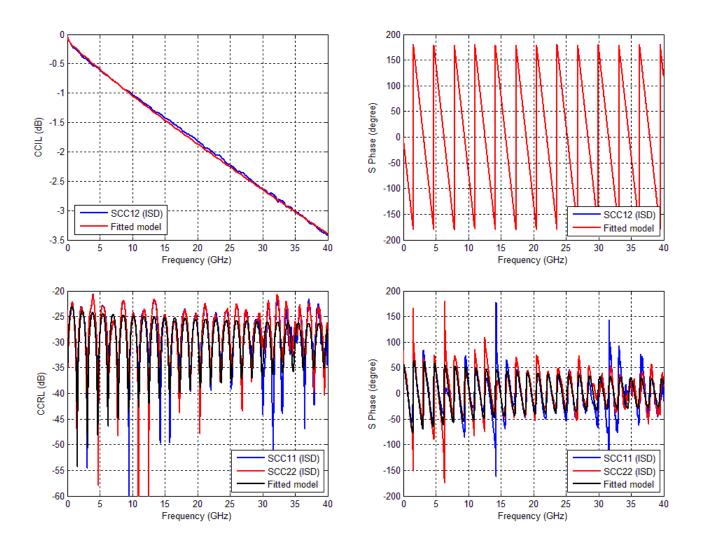

### Matching CCIL and CCRL

## Matching TDT and TDR

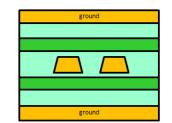

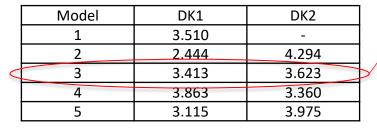

### **Comparison of Models 1 to 5**

Model 1 cannot match FEXT. Models 2 to 5 can match all IL, RL, NEXT, FEXT and TDR/TDT very well.

Model 1

ground

ground

Model 5

Model 3

Model 4

DK2

DK2>DK1 because of positive-polarity FEXT

At 10 GHz

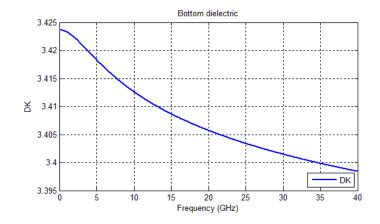

#### Extracted DK1 and DF1 Model 3

$\varepsilon_{\infty} = 3.27929$   $\Delta \varepsilon = 0.144348$  m1 = 9.58619m2 = 15.4109

$$\varepsilon = \varepsilon_{\infty} + \Delta \varepsilon \cdot \frac{1}{m_2 - m_1} \cdot \log_{10} \left( \frac{10^{m_2} + i \cdot f}{10^{m_1} + i \cdot f} \right)$$

$$= \varepsilon_r \cdot (1 - i \cdot \tan \delta)$$

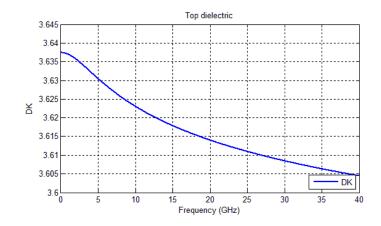

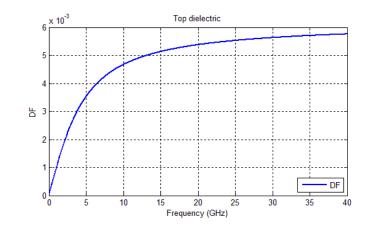

#### Extracted DK2 and DF2 Model 3

$\varepsilon_{\infty} = 3.46724$   $\Delta \varepsilon = 0.170196$  m1 = 9.58715m2 = 14.8352

$$\varepsilon = \varepsilon_{\infty} + \Delta \varepsilon \cdot \frac{1}{m_2 - m_1} \cdot \log_{10} \left( \frac{10^{m_2} + i \cdot f}{10^{m_1} + i \cdot f} \right)$$

$$= \varepsilon_r \cdot (1 - i \cdot \tan \delta)$$

#### Extracted effective conductivity Model 3

$\sigma = 5.8 \times 10^7 \text{ S/m}$  $R_q = 0.324321 \,\mu\text{m}$

# Length- and frequency-scalable models can now be created.

# Summary

- Accurate de-embedding is crucial for design verification, compliance testing and PCB material property (DK, DF, roughness) extraction.

- Traditional de-embedding methods can give noncausal errors in device-under-test (DUT) results if the test fixture and calibration structure have different impedances.

- In-Situ De-embedding (ISD) addresses such impedance differences through software instead of hardware, thereby improving de-embedding accuracy while reducing hardware costs.

#### Reference

- C.C. Huang, "Fixture de-embedding using calibration structures with open and short terminations," US patent no. 9,797,977, 10/24/2017.

- C.C. Huang, "In-Situ De-embedding," EDI CON, Beijing, China, 04/19 to 04/21/2016.

- C. Luk, J. Buan, T. Ohshida, P.J. Wang, Y. Oryu, C.C. Huang and N. Jarvis, "Hacking skew measurement," DesignCon 2018, 01/30 to 02/01/2018, Santa Clara, CA.

- H. Barnes, E. Bogatin, J. Moreria, J. Ellison, J. Nadolny, C.C. Huang, M. Tsiklauri, S.J. Moon, V. Herrmann, "A NIST traceable PCB kit for evaluating the accuracy of de-embedding algorithms and corresponding metrics," DesignCon 2018, 01/30 to 02/01/2018, Santa Clara, CA.

- J. Moreira, C.C. Huang and D. Lee, "DUT ATE test fixture S-parameters estimation using 1x-reflect methodology," BiTS China Workshop, 09/07/2017, Shanghai, China.

- J. Balachandran, K. Cai, Y. Sun, R. Shi, G. Zhang, C.C. Huang and B. Sen, "Aristotle: A fully automated SI platform for PCB material characterization," DesignCon 2017, 01/31-02/02/2017, Santa Clara, CA.